芯測是少見的台灣EDA+IP的公司,我在興櫃第一天就開始購入,可能漲太多了,最近有朋友開始問我對芯測的看法,我簡單講一下。芯測的產品主要用在IC設計階段,在實際送到晶圓廠生產(Taoe out)前跟著檢測流程「偵測」記憶體錯誤並「修復」錯誤的工具。芯測是清大LaRC實驗室博士班在2009年出來創業,原叫厚翼科技,後來原創辦團隊離開,由現任董座與晶心科前副總接手總經理,一開始就鎖定修復測試解決方案發展,2013取得清大兩項技術授權與專利,一路以來都在研發與累積專利,2017推出BRAINS的產品,2018年推出現有START的產品方案,2019推出BZ-BIST,START與BZ-BIST是目前主要兩個測試工具的產品線,BZ-BIST是應用在小範圍的測試或學術單位,START系列針對SoC,是貢獻主要營收的產品線。

我認為芯測面臨幾個趨勢上的順風:

- EDA工具由美國廠商壟斷,中美貿易戰致中國正處在國產替代的趨勢中。

- IC Design House在設計IC時,正發生的趨勢是,傾向直接向IP公司購買晶圓廠認證的IP,取代自己重新設計,當終端公司能透過購買IP,或是協同設計ASIC兜出IP設計圖時,越來越傾向自行設計IC,如Apple的ARM M1晶片,預計在晶片迭代越來越快下,將加速EDA與IP產業發展。

- 在以上兩個趨勢下,芯測挑選了記憶體修復的利基市場,我認為是個好故事。IC設計的EDA相對複雜,尤其在異質整合的趨勢下,芯測發展的新型態記憶體修復檢測,符合SoC與未來3D IC趨勢,未來記憶體密度與佔晶片面積都會增加,EDA大廠不見得有成熟的解決方案,看似是一個利基市場。

但同時也有許多營運的挑戰:

- EDA產品需要生態系支援,傳統做法是由學術圈慢慢累積,最終希望切入既有晶圓生產廠商與Design House生態系,由於一般EDA軟體也會有偵錯的功能,高階記憶體的偵錯是不是「關鍵」的利基市場,可以讓既有Design House採用芯測方案?有待芯測努力與驗證。

芯測是做什麼?

目前是亞洲唯一以EDA+IP提供記憶體測試與修復解決方案的供應商,重點在於如何幫客戶在IC設計過程中「減少記憶體的錯誤」與「降低開發成本與時間」。

讓我試著簡單講一下芯測的定位,芯測不是用來「設計NVM」的EDA Tool,應定位在「可測性設計DFT Tool」,降低IC開發成本與量產成本,競爭對手主要是內建在設計NVM EDA大廠中的類似功能,由於這些EDA大廠有可能在先進製程上提供的偵錯工具有所不足,為芯測提供機會,實際上在哪個階段會使用芯測Tool,後面會提到。

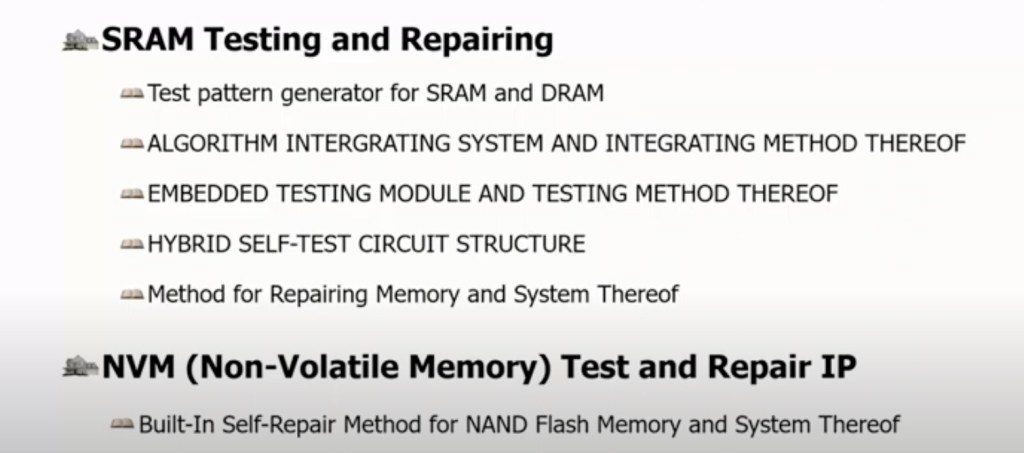

公司的競爭優勢在專利,專利佈局在中國、美國與台灣,根據2020年資料大約有34個記憶體測試專利,2021年取得全球第一個累加式的修復專利,次數可無限次修復,可看到芯測主要的專利都是演算法的專利(如下)。

芯測客戶是IC Design house、IP供應商與晶圓代工廠,主要協助IC設計的開發流程與提升良率,在異質封裝與SoC應用越來越廣泛的趨勢下,台灣主要晶圓代工廠相較南韓廠缺乏完整的記憶體佈局,也提供較小型的記憶體IP廠的潛在機會,另外值得留意的是,從10nm走到7nm,IC設計中軟體的成本多了35%,但從5nm走到7nm時, 軟體成本將多100%,整個EDA市場也將從2018的8.06 billion預計到2025複合成長率8.9%

產品分為EDA工具與客製設計兩大類。

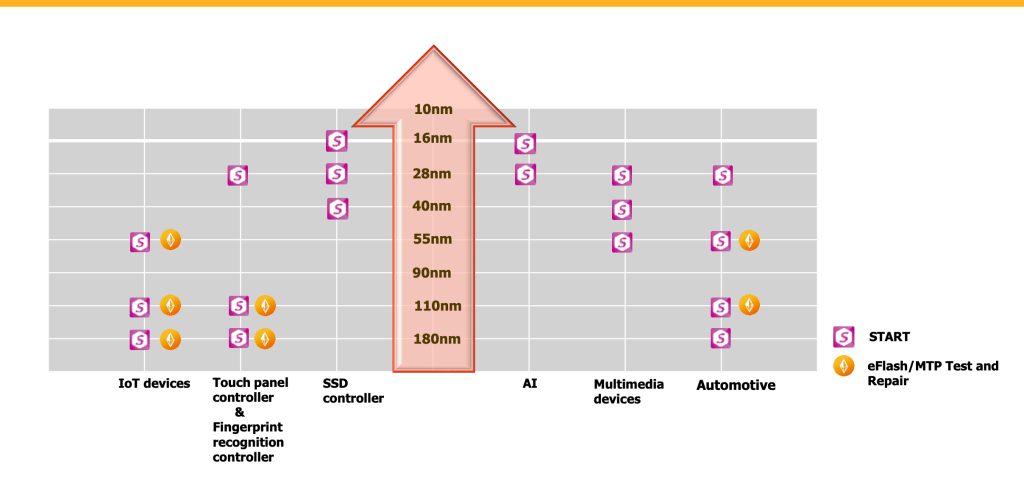

在EDA工具的部分,如果是開發內存記憶體<50個的MCU,芯測對應的產品是EZ-BIST,這通常用於小型專案、學術用的測試,比較正式的套裝產品是START V2,是針對SoC記憶體測試的完整工具,SoC中使用的記憶體常常是較新世代的如MRAM、RRAM或是eFlash,應用在AI、邊緣運算與車用等,目前芯測在MRAM測試演算法已經開發完成,RRAM的部分正與半導體製造商合作開發,現有銷售的產品線是eFlash。

客製化的部分依廠商的需求委託設計,如近期與祥碩合作POT。

IC House怎麼決定使用哪種EDA TOOL

在說明記憶體如何測試前,先談談IC設計流程。

IC Design的流程一開始是開SPEC,確定規格,這時會影響IC House在選擇EDA Tool的考量:

- 製造代工廠:每家代工廠的製程不同,美系的EDA廠商整合各家代工廠製程,Design House再依EDA廠商整理好的開發工具執行專案。

- 架構:SoC可能建立在許多不同的架構下,如FTP Trim\SLP等,IC House會先決定架構,再依架構使用不同EDA。

- 製程:NVM的製程通常在12nm~110nm都有,也是要先決定。

所以各家EDA Tool都會提供上述的選擇給IC Design House,IC Design House可以依照其終端產品的規劃選擇EDA,接著會做RTL(Register-transfer level),開出運算的邏輯。之後進行Synthesis,Synthesis這個步驟是透過EDA或其他廠商中既有的IP,來組合成你所需的產品,你可以把它當作是採購IP的過程,採購完後把它組合設計,組合好的設計就是"Netlist",可以視之為組好必備元件的草圖。

芯測的產品可支援RTL import與Netlist import,所以對IC設計廠商來說,芯測產品可用在IC設計的前端,如RTL(register-transfer level) design時,加入運算邏輯,或是IC設計的後端如synthesis後,跟著其他IP一起加入設計圖,組合成Netlist。

而在Netlist之後,進行placement & routing,這時就要確定晶片、標準元件的實體位置,以及其間的線路怎麼拉,這就關係到實際生產的狀況。

當晶片的實體位置、線路都已經設計好了,就會進行測試驗證,來確認這個設計圖的「運算」功能是否可以可行,是否有遺漏,如果OK,那就會Tape out,將這個設計圖交給IC製造公司如台積電。

而Tape Out前,就必須完成記憶體修復的動作,不然就來不及了。

當晶片Tape Out前必須進行測試與驗證,會使用自動測試設備(ATE),當晶片開始使用ATE自動測試時,這時候不管是在RTL或是Netlist時加入的芯測tool,就會啟動記憶體測試演算法,找出記憶體錯誤位置並修復,在跟原本客戶SoC電路整合在一起。

記憶體如何測試?芯測技術如何?

而記憶體到底怎麼修復?

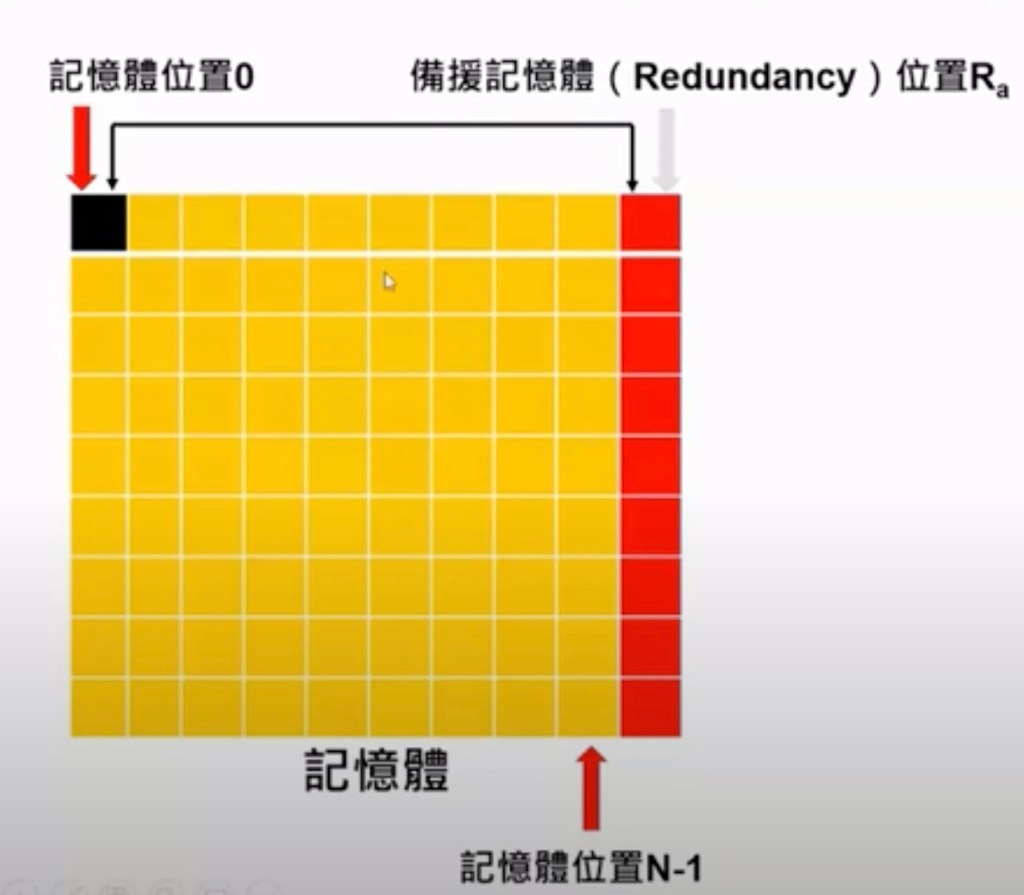

記憶體演算法主要是找出記憶體錯誤的位置,並記錄下來後透過「備援記憶體」進行置換,目前40nm的SRAM都會自帶備援記憶體,可以直接透過測試後修復,所以整個重點在於如何找到「錯誤」的位置,由於記憶體密度提升,靜電產生的干擾越多,「偵測的演算法」是整個過程中最重要的。

目前芯測的技術主要鎖定在sRAM與非揮發性記憶體(NVM),支援一次編程(OTP)與多次編程(MTP),用於eFLASH,目前MRAM測試演算法已經開發完成,RRAM的部分正與半導體製造商合作開發。

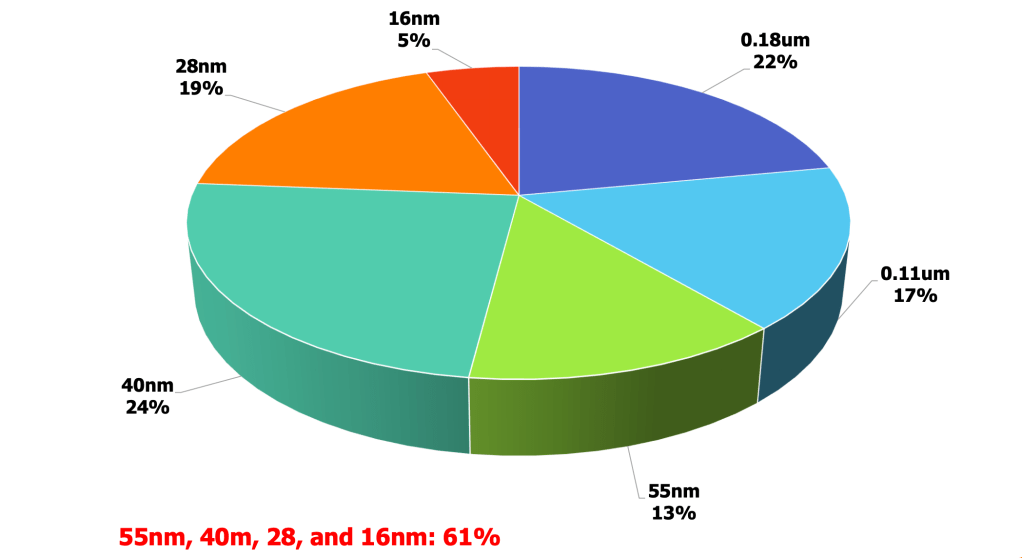

隨記憶體容量提升,錯誤的比例就會更大,偵錯就會越重要,目前如果是iSTART已經支援的ROM,可以直接支援,但如果是沒有支援的部分,芯測會針對記憶體的類型開發,芯測的製程應用集中在16nm~55nm的部分佔了61%。

另外,除了在晶片設計驗證與測試階段,採用ATE時使用芯測的工具外,芯測還有客製的EDA工具,如近期以切入祥碩,合作POT(Power-On Test)的方案,開機時可以偵錯,擴大記憶體測試與修復的應用範圍。

在製程與應用的分佈如下圖,蠻廣泛的分布在Auto、AI、SSD晶片、觸控指紋IC與IoT IC,車用在各個節點使用的機率很高。

客戶依照成本與時間考量,選擇Hard repair與soft repair,如果客戶有成本考量,但對開發時間較沒有急迫性,可以採取soft repair。

產業看法

芯測的產業是位處在IC Design的上游,最上面是IP Firm如ARM、力旺、Synopsys、晶心科,IC Design House是如聯發科、聯詠、瑞昱等會向IP Firm買IP後設計IC,設計完後,在轉給台積電、聯電等代工製作IC前,有可能會向芯測購買記憶體測試工具,來偵錯。

在競爭的部分,主要EDA廠商都有NVM EDA TOOL,裡面多少都有偵錯的程式,舉例來說,Synopsys產品DesignWare也是針對NVM的IP,支援一次編程(OTP)、少量編程(FTP)與多次編程(MTP),並已通過車用等級的驗證,產品簡介在此,另外,有些IC Design House自己也具有偵錯的能力,所以不見得會需要外部的偵錯Tool。

芯測的營運模式:

目前芯測服務的範圍不是讓客戶來設計NVM的EDA Tool,而是設計過程中用來偵錯的,芯測與客戶的合作模式有三種:

- Project:單次使用權,客戶可將芯測IP用於開發單一晶片,收入有License Fee與Royality兩類。

- Token:一次購買特定年限多次合約,於某年限用在多晶片開發案,收入也是License Fee與Royality。

- Licence:分為兩類:一次簽訂多年合約(Multi-Years)或是買斷(Pereual),兩者都不限使用次數,收入來源是授權金與維護費。

目前營收很不高,98%來自licence fee,維護費僅2%。

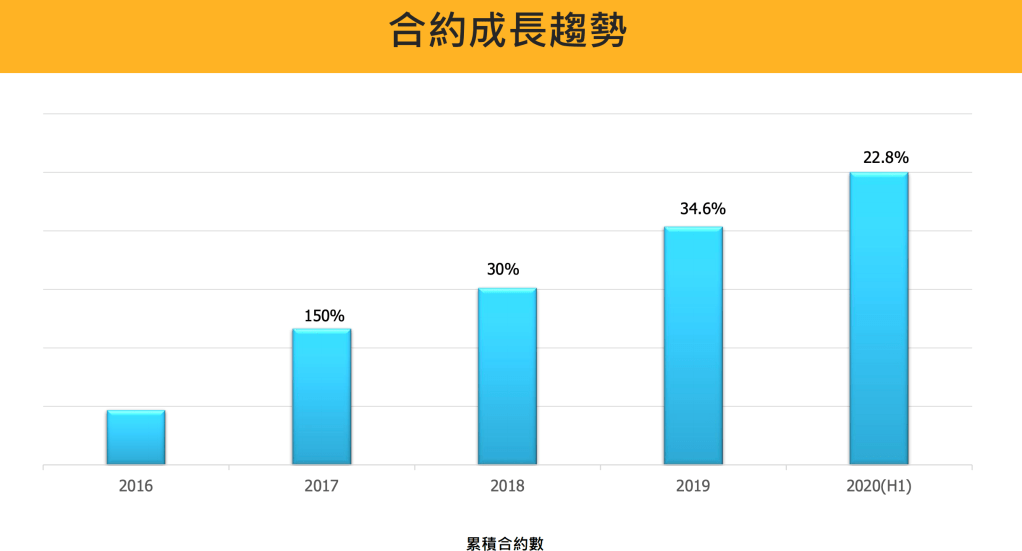

合約成長的部分,如下圖,截至2020年H1為止大概成長都在20~30%之間。

芯測的經營歷史?

技術、產品面與趨勢相較之下能簡單了解概貌,但在經營團隊的部分,這是我唯比較沒有把握的地方,原始的創始人已經離開。

芯測原是厚翼科技,是由創辦人刑育肇與鄧力銘兩位清大LaRC實驗室的博士創立,2016~2018年時優群有小量持股,2017年時由晶心科、聯電與聯陽出身的王炳興擔任負責人,而在2018年時陳冠豪擔任負責人至今,陳冠豪董事長專長在投資初創公司,入主厚翼後更名回芯測,持股比例也不高,僅1.57%(約353張),不過總經理賴俊澤倒是2017年至今都還在,賴俊澤出身晶心科副總,持股1.33%(約300張),董事會成員看起來都是投資界的前輩,獨立董事來自中租與宏觀微電子。

初期芯測的客戶為聯陽,後來逐漸擴展,包含M31、矽創、,國際客戶有ASIC LAND(韓)、Sequans(法)、國奇科技(中)、佩綸半導體(中)等,其中,M31持有芯測約400張股票,是非常正面的訊息,其中與M31的合作我認為非常重要,M31在2019時導入芯測SRAM Compiler IP的方案作測試,M31已經是TSMC主要的配合廠商,做高速運算與記憶體相關的IP設計,只是儲存類的佔比還不高。

關於芯測的看法

EDA軟體的商業模式很有趣, 當越多廠商加入使用EDA,EDA廠商能獲得更多的使用經驗而修正演算法,並導入Machine learning的模式,擴大其競爭優勢,所以芯測很積極舉辦webinar,並且開發學術用的套件BZ-BIST給學術單位以及研究生使用,這是蠻正向的。

我認為芯測產品,是在記憶體佔晶片面積比例越來越高時,佔IC成功與否的比重越來越高,即使傳統EDA Tool附的或是IC設計團隊內部本來就有這類的工具,但你還是可能為了加快開發速度或是降低量產風險,再使用芯測的工具除錯,除了可加速流程,也可提高準確度,如果價格合理,我認為IC Design House採用機率算高。

打個比方,就是你PC作業系統已經內建掃毒與防火牆,但你還是會去下載防毒軟體的意思,這個趨勢會不會真的發生,值得觀察,我認為機率還算高。

股價已經反應很多,這檔股票興櫃發行價才35,我在80元以上就沒有再加碼,不過暫時應該也還不會賣光,畢竟是新產品與新應用,業績需要時間慢慢反應,究竟是會變成一匹黑馬還是像億而得這樣?要觀察,但產品符合產業趨勢與利基市場,就看經營團隊如何推動。

回顧芯測近期股價,再比較當年M31,M31是智原總經理出來創業,成立隔年就是台積電供應鏈,營業額破5億才興櫃,對芯測來說,股價上漲的很快,只是我不明白為何公司要那麼快安排上櫃,是公司對營運很有信心嗎?屆時就知道,只是上櫃除了對股價maybe有幫助,有其他對營運有助益的地方嗎?以及經營階層的持股比例不高,也可能我調查不夠深入,但這是我比較有疑慮的地方。

Anyway,這已經是尚可的報酬了。